Helsinki University of Technology Department of Computer Science and Engineering Laboratory of Information Processing Science Espoo 2004

TKO-C93/04

# **Proceedings of Seminar on Real-Time Programming**

Vesa Hirvisalo (ed.)

TEKNILLINEN KORKEAKOULU TEKNISKA HÖGSKOLAN HELSINKI UNIVERSITY OF TECHNOLOGY TECHNISCHE UNIVERSITÄT HELSINKI UNIVERSITE DE TECHNOLOGIE D'HELSINKI

Helsinki University of Technology

Department of Computer Science and Engineering

Laboratory of Information Processing Science

P.O. Box 5400

FIN-02015 HUT

Espoo

Finland

Keywords: real-time programming, programming tools

Copyright © 2004 Helsinki University of Technology

ISBN: 951-22-7456-6 ISSN: 1239-6907

# **Preface**

Real-time programming is an art of creating computer software, whose timing behavior is predictable. Typically, real-time software systems are embedded systems, and vice versa. Such systems are very common – it has been estimated that 99% of all software applications are embedded. Real-time systems include communication systems, signal processing systems, control systems, databases, etc. They vary from small intelligent cards (or tags) though automobiles and airplanes to huge system, e.g., those used by military forces in battlefields.

Real-time software systems are often very complex. Typically, they consist of a number of interacting processes that must be synchronized in a predictable way. It is hard to implement the processes in a way that makes task execution times predictable. Because of such problems, real-time programming seems inherently difficult. Productivity of programming can be very low. For safety-critical applications (for which timing guarantees are a must), the productivity of the programming work can be a few lines of code per a day and a programmer.

Programming language development was very active during the 1970's and 1980's. Real-time programming was also considered. A number of programming languages were developed. The languages concentrated on the various aspects of real-time programming, e.g., worst-case execution time guarantees or incorporating process and synchronization abstractions.

Most of the languages developed for real-time programming did not reach application programming or have died away. Only Ada seems to have survived – and, its future is somewhat unclear, too. The current way of writing real-time applications seems to be the use of C language with process and synchronization mechanisms of a real-time operating system (RTOS). The number of real-time operating systems used is huge, and many of them do not conform with any standard (e.g., RT POSIX).

The Laboratory of Information Processing Science at Helsinki University of Technology organized a seminar on real-time programming during autumn 2004. The goal of the seminar was to discuss the options available to real-time programming (in addition to the C&RTOS combination). These proceedings include some of the work presented in the seminar.

The seminar consisted of three sessions. The first session of the seminar discussed Real-Time Java, which seems to be the current hot topic inside real-time programming. The second session discussed Ada and object-oriented programming, because the new Ada 2005 work is becoming available. For the third session, we wanted to have a specialized aspect of programming (to be compared with the general purpose programming languages). Because of the success of statecharts and the availability of tools generating production-quality code from statecharts, state-based programming was selected as the topic of the third session.

Espoo, December 2004 Seminar chair

Vesa Hirvisalo

# **Contents**

# **Session on Real-Time Java**

| Introduction to Real-Time Java                                       |    |

|----------------------------------------------------------------------|----|

| Aleksi Ahtiainen                                                     | 1  |

| Threads and Scheduling in Real-Time Specification for Java Framework |    |

| Ville Likitalo                                                       | 9  |

| Session on Ada and Object-Oriented Development                       |    |

| Introduction to Real-Time Programming with Ada'95                    |    |

| Juha Tukkinen                                                        | 15 |

| Using Rational Rose and Rational Rose RT in Real-Time Development    |    |

| Timo Toivanen                                                        | 21 |

| Session on State-Based Programming                                   |    |

| Introduction to Statecharts in Design of Reactive Systems            |    |

| Mikko Byckling                                                       | 27 |

| Visual Programming Tools and Code Generation for Real-Time Systems   |    |

| Samuel Siltanen                                                      | 35 |

| On Formal Modeling of Hybrid Systems                                 |    |

| Antti Kantee                                                         | 43 |

# Introduction to Real-time Java

Aleksi Ahtiainen Helsinki University of Technology Laboratory of Information Processing Science P.O.Box 5400, FI-02015 TKK, Finland Aleksi.Ahtiainen@tkk.fi

#### **Abstract**

Since the late 1990s several real-time extensions to Java programming language have evolved. RTSJ, the Real-time Specification for Java, has been the main subject of research and implementation work. This article introduces the current contents, future challenges and existing implementations of the RTSJ. Other real-time related Java technologies and their relationship with RTSJ are then introduced briefly.

# 1 Introduction

Java programming language has achieved its major success as a general purpose portable programming language. It is not applicable for real-time programming as such. Reason for this is Java's lack of real-time features like accurate timing, asynchronous transfer of control and predictability. The lack is currently actively being solved by specififying extensions to Java.

Purpose of this article is to introduce the current research and specification work of real-time programming in Java. The article is aimed at computer scientists and engineers who are planning to use Java for real-time applications or are planning to join the real-time Java research community. The article assumes that the reader already has basic understanding of real-time systems and experience in Java programming.

Second chapter introduces and demonstrates one realtime Java related technology, real-time specification for Java (RTSJ), in detail. The third chapter provides an overview of the future challenges and possible research areas related to the RTSJ. Currently existing implementations of the RTSJ are described in chapter four. Chapter five introduces other real-time Java related technologies and their relation to the RTSJ. The article is concluded in chapter six.

# 2 The Real-time Specification for Java (RTSJ)

The real-time specification for Java defines a class library and a virtual machine extension to Java. One of the main goals of the RTSJ specification is to add real-time capabilities to Java without any additions to the language itself. The aim is to create a specification with good backwards compatibility and minimal semantical changes. The specification also defines interaction features between non-, soft- and hard real-time threads within the same virtual machine. This is important since it is very common to have real-time constraints only for parts of an application. [15]

RTSJ is developed as Java community process (JCP) and version 1.0 [10] was published in 2001 as a Java specification request (JSR). Version 1.0.1 [11], which mainly clarifies some semantics, was published and accepted by the JCP working group in August 2004. Its final release is still pending on the reference implementation (RI) and technology compatibility kit (TCK) updates.

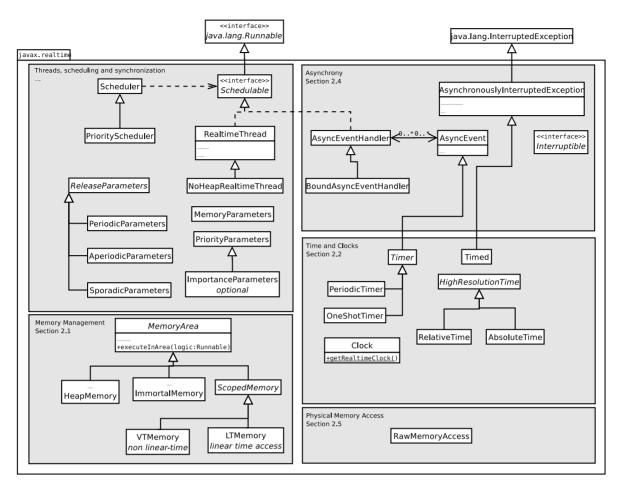

Figure 1 describes the main new Java classes introduced by RTSJ. Here is a short summary of the main RTSJ features. All of them are described in more detail in the following subsections. [10]

- Memory management with scoped memory regions

- · Accurate time and execution clock

- Schedulable objects, a priority scheduler for them and a framework for dynamic feasibility analysis in schedulers

- Asynchronous interrupts and asynchronous transfer of control

- Priority inheritance algorithm for preventing priority inversion of synchronized blocks

- Direct memory access

Figure 1. Main RTSJ classes

# 2.1 Memory Management

Perhaps the most controversial new feature of RTSJ is the introduction of scoped memory regions. Scoped memory regions are separate memory areas outside the garbage collected heap memory. Therefore real-time dynamic memory allocation can be done without worrying about garbage collection delays. The scoped memory regions are similar to method call stacks, but they are handled explicitely. The idea is that threads can enter and exit scopes and when all threads have exited a certain scope all the allocated objects in the scope are freed by the virtual machine. The scopes can also be nested within other scopes.

All the memory region types are represented by abstract MemoryArea class and the scoped regions are represented by its abstract subclass ScopedMemory. The two actual subclasses of ScopedMemory are LTMemory for memory allocations which assumes linear time complexity of allocations and VTMemory for the situations in which linear time is not a necessity. Code can be run in a specified scope

by incorporating the code in a new Runnable object and passing it as a parameter to MemoryArea.enter() or MemoryArea.executeInArea() methods.

It is still possible to use the garbage collected heap memory in non real-time parts of RTSJ applications. The heap memory is represented by a singleton subclass of MemoryArea called HeapMemory. There is also a memory region represented by subclass ImmortalMemory which can be used for static allocation of objects that are never freed while the application is running.

The semantics of the scopes are somewhat complicated, because referential integrity must be assured by the JVM. Therefore it is only possible to have memory references from the nested scopes to the parent scopes and not vice versa. References from immortal or heap memory to scoped memory regions are also forbidden.

#### 2.2 Time and Clocks

Common Java time classes are not accurate enough for real-time applications. Therefore RTSJ introduces new classes with accuracy up to nanoseconds. There are separate classes for relative time (RelativeTime) and absolute time (AbsoluteTime). The new time classes can be used in timing events and also with sleep() in the RealtimeThread class. The virtual machine's global real time clock is always available through call to Clock.getRealtimeClock().

There are a couple of ways to time events to happen at specified time in the future. The new Timed class is a subclass of AsynchronouslyInterruptedException and with it timers can be fired in the RTSJ's asynchronous transfer of control (ATC) framework. RTSJ's more advanced event handling framework can be used with class Timer's two subclasses OneShotTimer and PeriodicTimer. They all inherit from the AsyncEvent abstract class. Asynchronous transfer of control and event handling are described in more detail in section 2.4.

#### 2.3 Threads, Scheduling and Synchronization

RTSJ introduces the concept of schedulable objects which implement the new Schedulable interface. Schedulable objects can be threads or event handlers. The threads are implemented in two different classes, one for soft real-time threads (RealtimeThread) and another for hard real-time threads (NoHeapRealtimeThread). The latter is not allowed to use the garbage collected heap memory and therefore its execution deadlines are never missed due to garbage collection delays. The scheduler is also always able to pre-empty possible background garbage collector when NoHeapRealtimeThread needs to be run, because it does not use the garbage collector. Also RTSJ's event handler class, AsyncEventHandler implements the Schedulable interface (see section 2.4).

Three types of parameters are passed to new schedulable objects at construction. The parameters are specified using separate placeholder classes. Class MemoryParameters specifies memory usage limits for the new thread and subclasses of SchedulingParameters specify the thread's priority. Subclasses of ReleaseParameters can be used to specify the timing limits. The timing limits can define the schedulable object either as periodic, aperiodic or sporadic (classes PeriodicParameters, AperiodicParameters and SporadicParameters respectively).

The last method call in periodic threads must be waitForNextPeriod(), which blocks the thread until the start of its next execution. Depending on the scheduler

implementation, the method can return an indicator that a deadline miss has occurred, and the application can then react accordingly. Unfortunately there is no such way to detect deadline misses of aperiodic or sporadic threads.

RTSJ defines a framework for schedulers with dynamic feasibility analysis but does not specify an implementation. RTSJ specifies one scheduler which every implementation must implement. This scheduler is a priority scheduler with priority inheritance algorithm for priority inversion prevention. A scheduler with priority ceiling algorithm is defined in the specification, but it is optional to implement.

Objects in hard real-time and other domains of an application often need to communicate with each other. Straightforward method call communication would introduce possible garbage collection delays into the hard real-time domain and this must not be allowed. Therefore RTSJ specifies non-blocking queues for this communication (WaitFreeDequeue, WaitFreeReadQueue and WaitFreeWriteQueue).

#### 2.4 Asynchrony

RTSJ defines two basic asynchrony methods, asynchronous event handling and asynchronous transfer of control (ATC). The event handling framework is implemented by asynchronous events of class AsyncEvent. They can be bound to several schedulable objects, AsyncEventHandlers. All the handlers are called when the AsyncEvent's fire() method is called. The virtual machine may also implement event handling for external events like physical interrupts. These can be bound to AsyncEvents by using its method bindTo(). By default the virtual machine is allowed to use a single thread for several AsyncEventHandlers. Class BoundAsyncEventHandler can be used, if the application needs a dedicated event handler thread for some event type.

ATC is needed in order to have fast response times to certain events, like error situations or application Also some decision making can be mode changes. time-dependent. For example the application might be allowed to iteratively calculate better results until an external event happens. RTSJ implements ATC within the Java exception handling framework. Common Java threads do not guarantee immediate stop of thread execution when the thread's interrupt() method is called. RTSJ's RealTimeThread.interrupt() method does guarantee immediate handling of exception AsynchronouslyInterruptedException when it is called from some other thread. The methods which support this behavior must be identified by "throws Asyn-If the chronouslyInterruptedException". interrupt () method is called when the thread to be interrupted is outside such method, the interruption is handled immediately after the thread enters or returns to another method with the throws clause.

RTSJ also specifies a somewhat more structural way of specifying threads as asynchronously interruptible. A class can implement the Interruptible interface and define method interruptAction() accordingly. After this the interruptible thread can be started by calldoInterruptible(Interruptible intmethod of Thread) some AsynhcronouslyInterruptedException ohject. Then the interruptAction() method is called by the virtual machine immediately whenever the asynchronously interrupted exception's fire() method is called.

#### 2.5 Physical Memory Access

Many real-time applications are embedded applications that must have access to physical memory in order to implement hardware interfaces like drivers. RTSJ specifies a restricted way of accessing physical memory regions supported by the virtual machine implementation. In addition to regular MMU memory the virtual machine can specify regions for special purposes, like IO vectors. Is is only possible to use primary types (byte, int, etc.) in the raw physical memory. Class RawMemoryAccess specifies the methods for accessing all the basic types.

# 2.6 Example Program

There is a simple example RTSJ program in figure 2 on page 8. The program illustrates some of the RTSJ features. It creates a new periodic thread and illustrates how the method RealTimeThread.waitForNextPeriod() can be used to wait for the next period and to notice a possible deadline miss.

# 3 Future Work and Challenges of RTSJ

RTSJ is not a complete or optimal solution to all Java real-time programming needs. Some completely different approaches have been specified in other real-time Java technologies (see section 5) and several future challenges have been recognized in the current RTSJ [15] as described below. In addition to specification work, efficient implementations of RTSJ are naturally needed, if it is to gain widespread utilization. Compilers with static analysis for scoped memory regions and run-time environments with minimized ATC- and event handling overheads are a definite necessity.

The scheduling framework in RTSJ lacks many features, which would be beneficial for real-time development. Many

applications use several different schedulers at the same time. RTSJ does not currently take this into account. It could incorporate some communication methods between simultaneous schedulers. The specification also does not handle deadline misses of aperiodic or sporadic threads, even though they might often occur especially in soft real-time applications. In many situations it would also be helpful, if some separate thread importance parameter could be used when the scheduler needs to decide, which deadline is the least harmful to miss. The dynamic feasibility analysis framework in RTSJ would also gain strength from having additional clocks, like CPU time and thread blocking time, specified. [15]

RTSJ does not currently specify any support for distributed or multiprocessor systems, even though these are important real-time application areas. There has been some work on specifying a real-time Java RMI framework [12], but no implementation currently exists.

Probably the biggest challenges in RTSJ are related to the introduction of scoped memory regions. It is difficult to use existing Java libraries with scoped memory. Referencing scoped memory has been recognized also as one of the biggest challenges in real-time RMI specification work. [12].

Some new scoped memory design patterns have been designed ([18] and [16]) in order to make it easier for Java programmers to start working with scoped memory. The main difficulty is the restriction of not having references from immortal or higher scopes to lower ones. It might be good to have some class libraries for handling this kind of weak references in RTSJ. [15] Programming could also be made easier by having separate reference counting scoped memory areas or recycling list classes specified in the RTSJ. [15]

In the future the need for scoped memory might be completely removed by efficient hard real-time garbage collection. This has already been implemented in the JamaicaVM RTSJ implementation. Better static compile time analysis would also make it possible to reserve space for dynamic allocation of objects directly in the method call stack. Then the scoped memory regions would be completely unnecessary. [17]

# 4 RTSJ Implementations

Several RTSJ implementations already exist and are also under constant development as the specification and developer needs evolve. The Java Community Process, which RTSJ specification has been using, demands a reference implementation (RI) and also a technology compatibility kit (TCK), which can be used to test other implementations. TimeSys has the task to implement these for RTSJ [6]. Their RI and TCK have been developed to run compliantly on

TimeSys' own Linux distribution and also run with some hard real-time functionality loss in other Linux distributions.

TimeSys has also a commercial Linux implementation of RTSJ, called JTime. [7] In addition to the mandatory RTSJ features, it includes support for the dynamic feasibility analysis as specified in the RTSJ scheduling framework. The implementation is currently only supported with TimeSys Linux on PowerPC and IA-32 (x86) processor architectures.

JamaicaVM is another commercial RTSJ implementation. [19] In addition to RTSJ requirements it has hard real-time garbage collector. [17] Unlike TimeSys' implementation, JamaicaVM has been ported to several specialized real-time operating systems (VxWorks, Linux/RT, embOS, QNX, EUROS, ThreadX) and several processor architectures (x86, PowerPC, Sparc, RC32, StrongARM, NEC v850, Net+ARM). It also runs as non real-time virtual machine on common Linux, SunOS and Windows, which makes development and functionality testing easier.

GNU GPL licensed RTSJ implementation, jRate, is also under development. [14]. It is implemented as a compiler front-end and extended runtime system to the Gnu Compiler for Java, GCJ [2]. It is a research project which is being developed on x86 Linux, but should run on any POSIX compliant operating system.

Naturally Sun Microsystems also has a big role in the possible widespread adoption of RTSJ. Sun currently does not have its own RTSJ implementation, but is developing RTSJ JVM on top of a HotSpot JVM in project Mackinac [8]. Sun Labs, NASA's Jet Propulsion Labs and Carnegie Mellon University are also cooperating in an RTSJ adoption project Goldengate [3]. The project aims to implement a software called Mission Data System for use in future Mars missions.

# 5 Other Java Real-time Technologies

In addition to RTSJ several other real-time Java technologies have evolved since the late 1990s. There is no established standard yet. The following sections shortly introduce some of these technologies and their relationship with the RTSJ.

#### 5.1 Java 2 Micro Edition (J2ME)

Java 2 Micro Edition does not specify real-time features, but due to its current importance in embedded Java development, it deserves a short introduction here. Idea of Sun's J2ME specification work is to standardize a subset of parts of the Java language and libraries which are usable in embedded devices like mobile phones. Main goal has been to minimize the memory consumption of the Java virtual machine. [5]

J2ME has been a successful technology and many companies have added their own real-time capabilities into their J2ME implementations. Sun's own CDC HotSpot (former C virtual machine, CVM) J2ME implementation does not provide real-time capabilities, though [4].

#### 5.2 Ravenscar Profile for Java

Ravenscar profile for Java is a highly restricted subset of RTSJ for high-integrity applications, like nuclear reactors. Its goal is to improve predictability, integrity and security of real-time Java by removing features with high overhead and complex semantics. The specification does not go as far as removing multi-threading features, since they are analytically well understood nowadays. Somewhat obscure name of the specification is inherited from similar ADA profile. Like RTSJ, Ravenscar profile tries to keep programs runnable also in pure RTSJ virtual machines. [20]

The profile divides program execution to separate initialization and mission phases. The former initializes the threads after which they are started and no more initialization is allowed. The memory management is much more restricted, garbage collection is not included and only immortal and linear-time memory allocation is allowed in mission phase. Also the complexities of scoped memory have been removed by removing scope nesting and scope sharing between threads.

Only periodic and sporadic threads (not asymmetric) are allowed and the framework for dynamic feasibility analysis has been dropped. Static feasibility analysis must be performed prior to running the application, and therefore there is no need for overrun or deadline miss handling. The fixed priority scheduler must implement priority ceiling emulation in order to prevent priority inversion when using synchronized blocks of code. Java's wait(), notify(), notifyAll() and sleep() methods have been completely removed. Also asynchronous transfer of control and timers have been removed from RTSJ in order to simplify scheduling.

The profile also defines several clarifying restrictions on the language constructs, for example expression evaluation must not depend on evaluation order. Therefore a specialized compiler with plenty of static code analysis is needed to implement the profile. Naturally also a high integrity Ravenscar Java virtual machine needs to be used.

# 5.3 J Consortium's Real-Time Core Extensions for Java

J Consortium published a competing real-time extensions to RTSJ in 2000. [22] There are no implementations of these core extensions yet. The main features in comparison to RTSJ are: [21]

- Focus on hard real-time instead of combining the soft and hard real-time domains like RTSJ does

- Attach to existing virtual machines instead of changing Java semantics

- Direct sharing of objects between hard real-time and traditional Java domains is specified according to design of ADA's protected objects

- Does not support the immortal or scoped memory areas like RTSJ. Instead specifies allocation regions with explicit allocations and deallocations. Also stack allocation can be used with static analysis support at the compile time.

- Performance oriented, the goal of the specification work has been to offerspeed comparable to C and C++ in addition to predictability.

Ravenscar-like high integrity profile is also being designed for core extensions, but it has not yet been published. [20]

# 5.4 Open Group's Real-time Java Standardization Work

Due to the competing specifications, Open Group has been given the task to create a new safety-critical Java specification. The goal is to unify between the RTSJ and the Core extensions. Target of the work is to submit a Java specification request (JSR), reference implementation (RI) and technology compatibility kit (TCK) to the Java community process (JCP) by second quarter of 2005. [13] There are no public reports on the progress yet.

# 5.5 Stand-alone Real-time Java Products

Prior to the current specification work some companies have published their own real-time Java solutions. For example PERC [9] embedded virtual machine provides some real-time capabilities but does not conform to the RTSJ. Ajile Java processor [1] provides on-chip Java virtual machine with support for only a subset of the RTSJ specification

#### 6 Conclusions

This paper has reviewed the current work on extending Java for real-time programming. It has described the real-time specification for Java (RTSJ) and shortly introduced other real-time Java technologies.

Java is not perfectly suitable programming language for real-time applications, but there is enough interest in developing it into one. Currently the real-time specification for Java (RTSJ) has the most momentum and has already several implementations. Existence of other specifications and implementations illustrates that the RTSJ is not the only solution to the difficulties introduced by real-time demands. Some new features of the RTSJ, especially scoped memory regions, have been shown to add plenty of semantical complexity in programming. Therefore Java programmers need to design and adopt new programming practices, at least until real-time garbage collectors get efficient enough to be used instead.

# Acknowledgements

The author would like to thank T-106.850 Seminar on Real-time Programming tutor Vesa Hirvisalo and course students for their helpful comments on the drafts of this paper.

#### References

- [1] aJ-100 Java processor. At http://www.ajile.com/, Referenced 2004-OCT-11.

- [2] GCJ GNU compiler for Java. At http://gcc.gnu. org/java, Referenced 2004-OCT-11.

- [3] Goldengate project. At http://research.sum.com/ projects/goldengate/, Referenced 2004-OCT-11.

- [4] J2ME CDC hotspot implementation. At http://java.sun.com/products/cdc-hi/index.jsp, Referenced 2004-OCT-11.

- [5] Java 2 platform, micro edition (J2ME). Published at http: //java.sun.com/j2me/, Referenced 2004-OCT-11.

- [6] Java reference implementation (RI) and technology compatibility kit (TCK). At http://www.timesys.com/index.cfm?bdy=java\_bdy\_ri.cfm, Referenced 2004-OCT-11.

- [7] JTime. At http://www.timesys.com/index. cfm?bdy=java\_bdy.cfm, Referenced 2004-OCT-11.

- [8] Mackinac project whitepaper. At http://research. sun.com/projects/mackinac/mackinac\_ whitepaper.pdf, Referenced 2004-OCT-11.

- [9] PERC. At http://www.aonix.com/perc.html, Referenced 2004-OCT-11.

- [10] G. Bollella, B. Brosgol, P. Dibble, S. Furr, J. Gosling, D. Hardin, M. Turnbull, and R. Belliardi. *The Real-Time Specification for Java*. Addison-Wesley, 2001. Published at http://www.rtj.org/.

- [11] G. Bollella, B. Brosgol, P. Dibble, S. Furr, J. Gosling, D. Hardin, M. Turnbull, R. Belliardi, A. Wellings, and D. Holmes. The real-time specification for Java, 2004. Published at http://www.rtsj.org/specjavadoc/book\_index.html, Referenced 2004-OCT-11. This version of the specification has been approved as a minor change on Aug 9 2004 but will not be final until Reference Implementation and Technology Compatibility Kit have been updated.

- [12] A. Borg and A. Wellings. A real-time RMI framework for the RTSJ. In *Proceedings of the 15th Euromicro Conference* on Real Time Systems. Euromicro, IEEE, Jul 2003.

- [13] J. Child. Real-time Java takes aim at embedded control. RTC Magazine, (August 2004), 2004. Published at http://www.rtcmagazine.com/home/article.php?id=100111, Referenced 2004-OCT-11.

- [14] A. Corsaro. jRate. At http://www.cs.wustl.edu/~corsaro/jRate/,Referenced2004-OCT-11.

- [15] P. Dibble and A. Wellings. The real-time specification for Java: current status and future work. In Object-Oriented Real-Time Distributed Computing, 2004. Proceedings. Seventh IEEE International Symposium on, pages 71–77. IEEE Computer Society, 2004.

- [16] P. F., F. J. M., H. D., and J. Vitek. Real-time Java scoped memory: Design patterns and semantics. In *Object-Oriented Real-Time Distributed Computing*, 2004. Proceedings. Seventh IEEE International Symposium on, pages 101–110. IEEE Computer Society, 2004.

- [17] S. F. The impact of realtime garbage collection on realtime Java programming. In Object-Oriented Real-Time Distributed Computing, 2004. Proceedings. Seventh IEEE International Symposium on, pages 33–40. IEEE Computer Society, 2004.

- [18] B. G., C. T., C. V., C. V., D. D., G. B., I. M, M. K., M. A., and R. K. Programming with non-heap memory in the real time specification for Java. In *Companion of the 18th annual ACM SIGPLAN conference on Object-oriented programming, systems, languages, and applications*, pages 361–369. ACM Press, 2003. Published at http://doi.acm.org/10.1145/949344.949443.

- [19] a. GmbH. JamaicaVM realtime Java technology. At http: //www.aicas.com/, Referenced 2004-OCT-11.

- [20] J. Kwon, A. Wellings, and S. King. Ravenscar-Java: a high integrity profile for real-time Java. In *Proceedings of the* 2002 joint ACM-ISCOPE conference on Java Grande, pages 131–140. ACM Press, 2002. Published at http://doi. acm.org/10.1145/583810.583825.

- [21] K. Nilsen and A. Klein. OTM Workshops 2003, Lecture Notes in Computer Science, volume 2889, chapter Issues in the Design and Implementation of Efficient Interfaces between Hard and Soft Real-Time Java Components, pages 451–465. Springer-Verlag Berlin Heiderlberg, 2003.

- [22] J. C. Real-Time Java Working Group. Real-time core extensions, 2000. Published at http://www. j-consortium.org/rtjwg/index.shtml, Referenced 2004-OCT-11.

```

import javax.realtime.*;

public class PeriodicThread extends RealtimeThread

public boolean done;

public PeriodicThread(PriorityParameters pri,

PeriodicParameters per)

super(pri, per);

this.done = false;

public void run()

int c = 0;

boolean deadlineNotMissed = true;

while (!done && deadlineNotMissed) {

System.out.println("Counter at "+c);

// Do other periodic actions

deadlineNotMissed = this.waitForNextPeriod();

if (!deadlineNotMissed) {

// Period deadline has been missed, handle the problem

System.out.println("Periodic thread is exiting");

public void setDone()

this.done = true;

class SimpleExample

public static void main(String[] args) throws InterruptedException

// Create and start a new periodic thread with 100 ms period

PeriodicThread t =

new PeriodicThread(new PriorityParameters(PriorityScheduler.MAX_PRIORITY),

new PeriodicParameters(null, new RelativeTime(100, 0),

null, null, null, null));

t.start();

Thread.sleep(50000);

t.setDone();

}

}

```

Figure 2. An Example RTSJ Program

# Threads and Scheduling in Real-Time Specification for Java Framework

# Ville Likitalo Helsinki University of Technology Laboratory of Information Processing Science liki@iki.fi

#### **Abstract**

This paper describes Real-Time Specification for Java<sup>1</sup> compliant virtual machine in general. Emphasis is around threads and scheduling with other areas only briefly mentioned. Real-Time requires some fundamental differences compared to normal Java, also most RT systems are embedded as well.

#### 1. Introduction

Real-Time Specification for Java extends Java <sup>TM</sup>virtual machine, making it possible to build Real-Time systems in Java. RTSJ specifies strict requirements on schematics of Real-Time operation but still maintains backward compatibility so that normal Java programs will work with RTSJ-compliant virtual machine aswell.

RTSJ specifies framework allowing scheduling required by real-time operation. Many details are left to be specified by implementation but the specification is strict enough that real-time requirements can be met but at the same time the specification is open enough to allow tailoring for specific problems or architectures.

# 2. Real-Time Specification for Java

Real-Time Specification for Java defines extensions necessary to facilitate Real-Time systems. RTSJ does not inhibit backward compatibility, normal Java-programs will also execute under RTSJ virtual machine. Also portability - One of the key features of Java - is to be preserved, but not at the expense of predictability of execution. [8]

# 2.1. Design goals

Primary design goals of RTSJ are the following: [8]

<sup>1</sup>RTSJ

- Predictable execution

- extensibility

- No semantic extensions to the Java language

- To allow variations in implementations

Secondary goal is "Write Once, Run Anywhere", in other words binary portability. [8]

#### 2.2. Scheduling

Because of different requirements in RT systems for scheduling and dispatching models RTSJ does not dictate scheduling. One base scheduler is required by the specification, but the specification is flexible enough to allow development of different models. [8]

### 2.3. Memory management

RTSJ regards automatic memory management as an important feature of Java. Definition of Garbage Collector <sup>2</sup> is open to accommodate any GC algorithm, but effects on execution, preemption and dispatching must be taken into account. [8]

# 3. Virtual Machine

First virtual machine<sup>3</sup> was a time-sharing system that offered multiprogramming and an extended machine with a more convenient interface than the bare hardware. Nowadays a modern Java VM is a bit different, but RTSJ VM resembles the original counterpart more. [15]

Normal Java VM running as a single process in host operating system<sup>4</sup> is at the mercy of the host OS while trying

<sup>&</sup>lt;sup>2</sup>GC

$<sup>^{3}</sup>VM$

<sup>&</sup>lt;sup>4</sup>OS

to guarantee execution times. Many RT systems are embedded and VM runs as sole process on top of minimalistic OS, or it is the OS itself. [1, 3]

VM offers the same benefits for RT systems with the addition of predicability of execution. But naturally correctness of the VM itself is hard to prove. [1, 8]

#### 4. Time

Time is fundamental measure in RT systems and the normal accuracy of milliseconds in Java is inadequate for RT systems. RTSJ defines presentation of Time in accuracy of nanoseconds, and also makes distinction between absolute and relative time. All time objects must maintain accuracy of nanoseconds and provide simple arithmetic operations. [8]

Further RTSJ provides RationalTime for efficient presentation of occurances during period, i.e. frequency. [8]

#### 5. Threads

Traditionally each process has an address space and a single thread of control. A thread has its own program counter and stack, but shares other resources with other threads within a process. [15]

RTSJ defines 2 types of threads that extend java.lang.Thread but have more precise scheduling semantics. Due to nature of RT systems, threads must be able to allocate memory from other areas than heap and provide semantics for handling asynchronous events. Extensions provided by RTSJ must only be available in the context of RealtimeThread, NoHeapRealtimeThread, AsyncEventHandler or BoundAsyncEventHandler. [8]

Main distinction between RealtimeThread and NoHeapRealtimeThread is that the later may not reference memory or objects in memory that is dynamically allocated, ie. maintained by GC. This allows NoHeapRealtimeThread to have higher priority than GC and interrupt execution of GC. [8]

The separation could also have been made by preserving priorities higher than GC for NoHeapRealtimeThreads and lower than GC for RealtimeThreads, but this does not place any restrictions on the priorities and illegal references can be detected at the time of compilation.

#### 5.1. RealtimeThread

RealtimeThread extends java.lang.Thread to hold parameters necessary for RT operation. Priority-preemptive dispatching model in Java is similar enough to the model used in many RT operating systems, but semantics were relaxed to allow execution on a wide variety of operating systems. [8]

### 5.2. NoHeapRealtimeThread

NoHeapRealtimeThread is a specialized form of RealtimeThread. It is provided for time-critical applications that must have priority higher than GC. Therefore logic contained within NoHeapRealtimeThread may never allocate objects from heap, or reference objects allocated in the heap. This way it has been made safe for NoHeapRealtimeThread to interrupt execution of GC. [8]

# 6. Synchronization

Avoiding priority inversion when sharing resources is very important in RT systems. Therefore RTSJ requires implementations to strengthen the schematics of the Java synchronized keyword. At least one algorithm that prevents priority inversion is required. RTSJ specifies the following algorithms. [8]

- Priority Inheritance

- Priority Ceiling Emulation

RTSJ defines that threads waiting on a mutex must be priority ordered, with threads with same priority behaving in FIFO<sup>5</sup>-manner. [8]

Also, RTSJ specifies wait-free queues for communication from RTSJ-scope with the traditional Java parts of a system. [8]

# **6.1. Priority Inversion**

Priority inversion in this case refers to a situation where a thread with higher priority is waiting on a mutex reserved by a thread with lower priority, but a thread in ready state which has higher priority than the thread reserving the mutex prevents the thread from running and releasing the mutex. [15]

## 6.2. Priority Inheritance

Priority Inheritance works by modifying priority of a thread owning the mutex. If a thread with a higher priority is waiting for the mutex, priority of the thread owning the mutex is raised to priority of the waiting thread if it was lower. After the thread releases the mutex its priority is restored back to normal. This ensures that a thread with lower priority may no longer prevent the thread owning the mutex from running. [11]

<sup>&</sup>lt;sup>5</sup>First In, First Out

### 6.3. Priority Ceiling Emulation

In Priority Ceiling Emulation a mutex is assigned a highest possible priority it is valid in. When a thread that has a priority lower than this set limit locks the mutex its priority is raised to the limit set for the mutex. When the mutex is released the priority of the thread is restored back to normal.

# 7. Scheduling

Scheduling means that when two different processes, or threads are at ready state, a scheduler must choose which one to run next. Events in RT system can be categorized as periodic or aperiodic. Scheduler must take care that time restrictions set upon the system are met. A RT system that meets the criteria in 1 is said to be schedulable. [15]

$$\sum_{i=1}^{m} \frac{C_i}{P_i} \le 1 \tag{1}$$

Where event i occurs with period  $P_i$  and requires  $C_i$  seconds of CPU time to handle each event.

There are two basic types of schedulers, static and dynamic. Static schedulers make scheduling decisions beforehand. This means that information about occurring events and work needed must be exact so that the scheduler can be tailored for the system. Dynamic schedulers do not suffer from this restriction but are more complex. [15]

# 7.1. Scheduling in RTSJ

Scheduler required by RTSJ is fixed-priority preemptive, however other schedulers may be provided. Schedulable objects are presented by RealtimeThread, NoHeapRealtimeThread and AsyncEventHandler or any object implementing Schedulable interface. RTSJ requires additional lower priorities that will be assigned to native Java threads. By default new threads inherit SchedulingParameters from their parent thread. [8]

It is also even possible to introduce several schedulers into one system, with perhaps different schedulers with each scheduling one type of tasks. However RTSJ does not specify any methods with which these different schedulers could communicate with each other. [8]

#### 7.2. PriorityScheduler

PriorityScheduler is the base scheduler required by RTSJ. Base scheduler is fixed-priority preemptive scheduler with 38 unique priority levels, 28 required for RT threads and rest for native Java threads. The following requirements are set: [8]

- Preempted threads may be placed in the appropriate queue at any position.

- A blocked thread that becomes read is added to the tail of any runnable queue for that priority.

- A thread whose priority is changed is added to the tail of the runnable queue for the new priority level.

The very exact manner in which queues are operated is left to the implementation, but RTSJ requires that the exact operation is documented. [8]

# 7.3. SchedulingParameters

Subclasses of SchedulingParameters provide parameters used by scheduler. RTSJ specifies PriorityParameters and ImportanceParameters and other classes may be specified if required by particular implementation of scheduler. [8]

Instance of PriorityParameters can be assigned for threads managed by schedulers that use a single integer<sup>6</sup> to determine execution order. [8]

Instance of ImportanceParameters can be assigned for threads to determine additional scheduling metric used in addition to priority level. This metric can be used e.g. in overload conditions to determine threads that are more important than others. RTSJ does not require base scheduler to take importance into account, but it is recommended that a simple extension is provided. [8]

#### 7.4. ReleaseParameters

ReleaseParameters is an abstract class defining release characteristics of threads. ReleaseParameters holds execution cost, deadline and overrun and miss handlers. Overrun handler is invoked if invocation of an object exceeds its assigned cost and miss handler if an object is still executing after its deadline has passed. RTSJ specifies PeriodicParameters, AperiodicParameters and SporadicParameters. [8]

# 7.5. Periodic events

PeriodicParameters indicates that a call to waitForNextPeriod() will be unblocked at the start of a each period, thus the object gets periodically executed. PeriodicParameters takes start time and length of the period as additional parameters. [8]

To schedule periodic events a timer must be set to match the period. Thread handling the periodic event must call waitForNextPeriod() and becomes blocked until timer unblocks the call after the period has exceeded. Overrun handler may be called if execution cost exceeded cost set in the

<sup>&</sup>lt;sup>6</sup>Priority level

parameters and deadline miss handler must be called if the deadline in set in the parameters was exceeded. [8]

# 7.6. Aperiodic events

Aperiodic Parameters characterizes an object that may become active at any time. Aperiodic events are usually triggered via interrupt by external events or internally in the program. [8]

For aperiodic threads the call into fire() is made when the launching event occurs. Again, overruns may be detected but deadline misses must be detected. [8]

### 7.7. Sporadic events

SporadicParameters is a notice to the scheduler that the object will release execution aperiodically but with a minimum time between releases. [8, 5]

Sporadic threads are handled in the same way as aperiodic threads, but due to nature of the event implementations are required to maintain to list of times when the event has occurred. For sporadic threads detection of deadline misses is not required. [8]

# 8. Feasibility Analysis

For static schedulers no new schedulable events are accepted during operations and feasibility analysis can be performed beforehand. That may include complex statistical analysis and simulation of the system, however dynamic schedulers are required to perform the analysis in real-time and no such methods are feasible nor data present. [8, 15, 5]

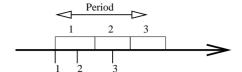

However, noting that applications are required to provide execution cost for real-time events and recalling 1 we note that the feasibility analysis is trivial for periodic events as the period must be known. Aperiodic and sporadic events can be added into the analysis by some elementary probability calculus provided that their probability is known. Although this means that the analysis is not proof for any selected period like illustrated in figure 8.

Here we assumed that performed calculations have no deadline requirements but even then we could see that the simple approach into the analysis problem is not nearly adequate. Restricting the analysis into periodic events means the solution is still easily calculated, but accounting for aperiodic and sporadic events requires more extensive analysis. [5]

Possible feasibility analysis algorithms include for example:

- Rate Monotonic Analysis

- Deadline Monotonic Analysis

- Queue Analysis

#### 8.1. Rate Monotonic Analysis

Rate Monotonic Analysis<sup>7</sup> was originally invented the beginning of '70s and later in '80s generalized enough to be practical. Original limitations of RMA were: [13, 10, 14]

- Fixed-priority scheduling

- Only periodical tasks

- Tasks do not synchronize

- Tasks do not suspend themselves

- Tasks can be instantly preempted

RMA is an analytic approach to predicting wether latency requirements set for the system are met. Execution and task parameters are used to calculate worst-case latencies for each thread and compared to the requirements set for the threads. Commonly revealed problems are priority inversions. [14]

The more general form of RMA is best suited for systems dominated by periodic or sporadic tasks for which time limits can be bounded without excessive variability. Systems in which WCET<sup>8</sup> are infrequent or there is no minimum interval between invocations are not best suited for RMA analysis. When dominating tasks are aperiodic, another analysis algorithm is needed. Although originally intended for off-line analysis, there are no reasons why RMA could not be applied on-line with modern computational capabilities. [14]

#### 8.2. Deadline Monotonic Analysis

Deadline Monotonic Analysis<sup>9</sup> is a method similar to RMA and suffers from the same limitations. In DMA tasks that have deadlines sooner are assigned higher priorities and probability that deadlines are met is increased by that way. Further, it can be shown that if a set of periodic tasks is schedulable, it is schedulable by deadline monotonic algorithm.

<sup>&</sup>lt;sup>7</sup>RMA

<sup>&</sup>lt;sup>8</sup>Worst-Case Execution Time

<sup>9</sup>DMA

If we examine the 3 different periodic tasks in 1 we can show that they fulfill the requirement in 1.

$$\sum_{i=1}^{m} \frac{C_i}{P_i} \leq 1$$

$$\frac{C_a}{P_a} + \frac{C_b}{P_b} + \frac{C_c}{P_c} \leq 1$$

$$\frac{0,05}{0,3} + \frac{0,2}{0,5} + \frac{0,15}{0,4} \leq 1$$

If we assume that all events a, b and c are simultaneously fired at time 0 rate monotonic scheduling fails to meet the deadlines. Events are handled by the order of their frequency, ie. a, c and b as last which fails to meet its deadline. With deadline monotonic scheduling the execution order is a, b and c as last and all deadlines are met.

#### 8.3. Queue Analysis

Queue analysis is required for systems dominated by aperiodic tasks. The analysis derives directly from queue theory and is based on the fact that the queueing system must satisfy 2 where  $\rho$  is the server utilization,  $\lambda$  the number of events per time unit and  $\mu$  the number of events possibly served in one time unit.

$$\rho = \lambda/\mu \le 1 \tag{2}$$

# 9. Asynchrony

Often external events dictate execution times in RT systems, thus RTSJ defines mechanisms to bind execution of program logic to internal and external 10 events. Further RTSJ specifies methods for asynchronous transfer of control and thread termination. An event may be fired by application logic or an event external to the system, such as hardware interrupt. [8]

# 9.1. Asynchronous Events

Asynchronous events are handled by AsyncEvent which corresponds to the event and its probability of occurrence.

Table 1 Different tacks

| Table I. Dillelelit tasks |       |       |          |  |

|---------------------------|-------|-------|----------|--|

| Task                      | $P_i$ | $C_i$ | Deadline |  |

| a                         | 0,3   | 0,05  | 0,1      |  |

| b                         | 0,5   | 0,2   | 0,25     |  |

| c                         | 0,4   | 0,15  | 0,4      |  |

Occurrence of the event is expressed by a call into fire() method. The fire() -method does not pass data for the handler, application needing to associate data with asynchronous events must do it by explicitly setting up a buffer.

An object subclassing abstract class AsyncEventHandler or BoundAsyncEventHandler is scheduled in response to an occurrence of an event. BoundAsyncEventHandler is used when it must be ensured that each event is handled by a separate thread. When the event occurs, all event handlers bound to the event are scheduled for execution. [8]

#### 9.2. Asynchronous Transfer of Control

Asynchronous Transfer of Control<sup>11</sup> is designed to allow efficient execution for a wide variety of RT systems. In RT systems there can be a large number of potential events with only a minimal number used at the same time, where dedicating a separate thread for each event seems excessive. RTSJ also allows program to bound an event to specific thread by BoundAsyncEventHandler. [8]

To provide better ATC RTSJ overloads the interrupt() method in java.lang.Thread offering nonpolling execution control. It is based on throwing, deferring and propagating exceptions. ATC uses AsynchronouslyInterruptedException<sup>12</sup> for operation and methods must indicate this by including it in their throws-clause where applicable. [8]

Program may initiate ATC by throwing AIE itself and are subject to receive AIE if it has been declared to be thrown by the method. Exception to this is when execution of such method is in synchronized context, in which case AIE is put into pending state and received after execution leaves synchronized context. Also constructors are allowed to declare AIE as thrown and are thus interruptible. Thread subject to receive an AIE must respond to that exception within a bounded number of byte codes and the worst-case response time must be documented. [8]

thread is interrupted in ATC AsynchronouslyInterruptedException is thrown once the thread is outside of a section in which ATC is deferred. Programmer may take advantage of this by using catchclauses or the low- and high-level systems provided by RTSJ. [8]

Potential problem of catch-all clauses

try

$$\{ \dots \}$$

catch (Throwable t)  $\{ \dots \}$

is worked around by requiring special schematics for catching AIEs. AIE is propagated forward unless handler calls happened() -method in the catch-clause. [8]

<sup>&</sup>lt;sup>10</sup>asynchronous

<sup>&</sup>lt;sup>11</sup>ATC

<sup>&</sup>lt;sup>12</sup>AIE

# 9.3. Asynchronous Thread Termination

Asynchronous thread termination works by the same mechanism as ATC, however threads are immortal as the termination would need to invoke methods that have AIE in theirs throws-clause. [8]

#### 10. Conclusions

RTSJ seems a flexible enough framework to allow development of a wide variety of Real-Time systems and solutions. Minimal implementation of the virtual machine as required by the specification allows development of Real-Time systems only in limited scope. The framework is general enough to allow for development of a virtual machine tailored to the special needs of application and it could well be impossible to develope a general-purpose virtual machine that would suit all different applications.

#### References

- [1] M. Barr and B. Frank. Java in Embedded Systems. *Embedded Systems Programming*, pages 24–32, May 1997.

- [2] B. J. Brosgol. Ada and Java: Real-Time Advantages. Embedded Systems Programming, Nov 2003.

- [3] B. M. Brosgol. Introduction to Real-Time Java. Embedded Systems Programming, Apr 2003.

- [4] F. Bruin, F. Deladerriere, and F. Siebert. A Standard Java Virtual Machine for Real-Time Embedded Systems. Proceedings of DASIA 2003 (ESA SP-532), 2003.

- [5] A. Burns and A. Wellings. Processing group parameters in the real-time specification for java. In On the Move to Meaningull Internet Systems 2003: Workshop on Java Technologies for Real-Time and Embedded Systems, volume LNCS 2889, pages 360–370. Springer, 2003.

- [6] H. Cai and A. Wellings. Towards a high integrity real-time java virtual machine. In On the Move to Meaningull Internet Systems 2003: Workshop on Java Technologies for Real-Time and Embedded Systems, volume LNCS 2889, pages 319–334. Springer, 2003.

- [7] P. Dibble. Real-Time Java Platform Programming. The Sun Microsystems Press, 2002.

- [8] G. B. et al. The Real-Time Specification for Java. Addison-Wesley, 2000.

- [9] E. Y.-S. Hu, G. Bernat, and A. Wellings. A Static Timing Analysis Environment Using Java Achitecture for Safety Critical Real-Time Systems. In Proceedings of 7th IEEE International Workshop on Object-Oriented Real-Time Dependable Systems (WORDS-2002), pages 64–71, Jan 2002.

- [10] C. L. Liu and J. W. Layland. Scheduling algorithms for multi-programming in a hard real-time environment. *Jour*nal of the Association for Computing Machinery, 20:40–61, Jan 1973.

- [11] R. Rajkumar, L. Sha, and S. Sathaye. Priority inheritance protocols: An approach to real-time synchronization. *IEEE Transactions on Computers*, 39:1175–1185, 1990.

- [12] M. Schoeberl. Restrictions of Javafor Embedded Real-Time Systems. In Proceedings of 7th IEEE International Symposium on Object-Oriented Real-Time Distributed Computing (ISORC 2004), pages 93–100, May 2004.

- [13] O. Serlin. Scheduling of time critical processes. In *Proceedings of the Spring Joint Computer Conference*, pages 925–932. American Federation of Information Processing Societies, 1972.

- [14] Sha, Klein, and Goodenough. Rate monotonic analysis for real-time systems. In Foundations of Real-Time Computing: Scheduling and Resource Management, pages 129– 155. Kluwer Academic Publishers, 1991.

- [15] A. S. Tanenbaum. Modern Operating System. Prentice-Hall Inc. 2001.

- [16] A. Wellings. Concurrent and Real-Time Programming in Java. Wiley, 2003.

# **Introduction to Real-Time Programming with Ada 95**

Juha Tukkinen

Helsinki University of Technology

Laboratory of Information Processing Science

P.O.Box 5400, FI-02015 HUT, Finland

juha.tukkinen@hut.fi

#### **Abstract**

Real-time programming is a very demanding task. The majority of current programming tools such as programming languages, operating systems and design tools are not suitable for real-time programming. When the system's correct behavior is also dependant on the timing of the computations, tools used must support this. This survey provides basic facts how Ada 95 can be used as a tool for real-time programming, instead of a tutorial of Ada 95 programming in general. This high level object-oriented language is still adequate for developing portable real-time applications. Having sophisticated built-in support for concurrency and real-time features, it is one of the very few realistic alternatives to C or assembler programming language in this domain.

#### 1. Introduction

The correctness of a real-time system's behavior is dependant also on the timing of the computation results, not just the correctness of the results themselves. These systems must be predictable in execution time and react within certain deadlines.

A major problem in real-time programming is the large variety of tools. Real-time programs need support from the language (compiler), operating system and the hardware. The high level of abstraction that the tools must provide are, for example, scheduling and memory allocation.

Ada 95 is a language designed to be used in real-time programming with its extensions. It can make use of the concurrency features of real-time operating systems or executives. The main goals in Ada design have been high reliability, flexibility, reusability and maintainability in safety critical environments [5].

In real life, Ada 95 has been used in banking and financial systems, information systems, air traffic management

systems, commercial aviation, commercial rockets, commercial imaging space vehicles, satellites, data communications, scientific space vehicles, railways, shipboard control systems, TV/entertainment industry, medical industry, general industry, military applications and by NASA. [4]

The structure of this article is as follows. The next chapter views the background and history of the Ada language with main focus on real-time programming features. Chapter 3 explains how the Ada 95 language supports concurrent programming. Chapter 4 describes how scheduling is done in real-time with Ada 95. Memory management is thought over in chapter 5. Chapter 6 covers different levels of communication. The last chapter concludes the article with a summary and a discussion of the possible future real-time features in Ada 0Y.

# 2 Background

Ada 83 had only preemptive scheduling based on static priorities. The problem of priority inversion was not solved. This means that threads with a lower priority might block higher-priority threads through the use of synchronization models. Also there was no model how task priorities interact with interrups and protected objects. The design was later on thought to be not enough portable and too restrictive.

There was an emerging need of support for dynamic priorities, better scheduling and tasking model design and more advanced timing features. The Ada 95 language extends Ada 83 by supporting these features and also for example abort-deferred regions and explicit synchronous and asynchronous task control protocols. [5]

In this article, real-time programming in Ada 95 is explained. The reader is presumed to have basic knowledge of the Ada language syntax and semantics. A good source to learn Ada from is for example *Ada Distilled* [8].

The core Ada language has no support for real-time features. However, some features, like concurrency support, not specific only to the real-time programming domain are

already built in the Ada 95 language. The Annex D in language reference manual [6] augments the core Ada language semantics by single solutions to problems in real-time programming.

Using these portable set of real-time capabilities features also poses a set of restrictions for the core language itself. These real-time features are invoked by using so called *configuration pragmas*. The semantics they correspond to are therefore only available to the one active partition of the program.

Next, the focus is in important features needed in realtime programming. Concurrent programming, scheduling, memory management and communication in task level and device level in Ada 95 are explained.

# 3 Concurrency support

Ada supports concurrency by multitasking and by distributed objects. Multitasking, called tasking in Ada, is implemented using only two types additional to the standard syntax and semantics of Ada. The semantics of these types, *task types* and *protected types* are augmented in Anneces C and D. Distributed programming is specified in the Annex E and it is not discussed in the scope of this article.

Because Ada has an integrated concurrency model, no external programming interfaces or specific operating systems support is needed. Concurrency is an essentially used feature in real-time programming, having a standard way to provide it improves portability.

An example program demonstrating both Ada concurrency features and its syntax in general can be seen in Figure 1. The trivial program runs two tasks, the first one prints out a sequence of numbers and the other one waits for user input to terminate the program.

#### 3.1 Tasks

A task is an concurrent active object and it can be either in executing or suspended state. A task has a *base* and an *active* priority.

The base priority is given to a task when it is created. It can also be dynamically set later. The active priority of a task changes more often, although it reflects the base priority. The active priority changes usually by *priority inheritance*. It is used when the task competes for resources, it determines the task's position in the priority queue. To be precise, the active priority of a task is the maximum of the inherited priorities. A task inherits another task's base priority.

*Critical regions* for tasks are accomplished with *do* parts. Until this critical region is finished, the calling task is suspended.

### 3.2 Protected objects

Ada does not use mutexes or semaphores for concurrency. On the contrary, the *protected object* mechanism is used to allow the design of self-locking, encapsulated objects.

A protected object has protected components and operations. This means that the implementation must ensure mutually exclusive access to the object across tasks. An example of an protected object is shown in Figure 4.

# 4 Real-time scheduling

The real-time scheduler is responsible how the previously discussed components competing for resources are selected to be run. Compared to scheduling in more traditional environments, real-time schedulers need static timing information like possible execution time boundaries beforehand. Their behavior has to be very predictable and reliable.

Real-time scheduling is specified by the task dispatching model in Annex D of the Ada language reference manual. The tasks are selected to be run based on priority-ordered ready queues. The scheduling is *preemptive*. Details on the history of priority-based scheduling theory in Ada can be found from [9].

# 4.1 Task dispatching

The basic idea behind this is that a task becomes a running task only when the resources needed are available and the task itself is ready. Resources like processors are allocated based on the active priority of a task. The task dispatching takes place on so called *dispatching points*. These points occur, for example, when a task blocks, becomes ready or gets terminated or preempted.

Each processor has a ready queue, an ordered list of ready tasks, per a priority value. A task is in this queue only if it is ready or already running. A task can be on more than one processor's ready queue but it can be only running on one processor.

The only standard task dispatching policy that must be implemented is FIFO\_Within\_Priorities. The policy covers details not described in the task dispatching model like when and where the task is put in the ready queue after certain events. It is described in detail in chapter D.2.2 in [6].

# 4.2 Priority inversion problem

The situtation, when a lower priority task prevents a ready task with a higher priority to be run, is referred to as the priority inversion problem. This is a highy unwanted

```

with Ada. Text_IO; use Ada. Text_IO;

procedure Task_Test is

Time_To_Quit : Boolean := False;

pragma Atomic(Time_To_Ouit);

task Multiplier_Task;

task Counter_Task;

task User_Task;

task body Counter_Task is

Increment : Integer := 1;

begin

while not Time_To_Quit loop

Put("Counter task: ");

Put_Line(Integer'Image(Increment));

Increment := Increment + 1;

delay 0.6;

end loop;

end Counter_Task;

task body User_Task is

Char : Character;

begin

loop

Get (Char);

Skip_Line;

if Char = 'q' then

Time_To_Quit := True;

exit;

end if;

end loop;

end User_Task;

-- main loop here

begin

100p

delay 1.0;

exit when Time_To_Quit;

end loop;

end Task_Test;

```

Figure 1. Example of an concurrent program in Ada 95

situation especially in the real-time domain as it can easily disturb the system's schedulability.

The priority inversion is the time a task remains at the head of the highest priority ready queue while a task that has a lower priority is executed. The time is implementation dependant and the maximum priority inversion must be documented by the Ada compiler specification.

As this is a big problem in real-time programming, Ada 95 programmer has means to minimize the risk of it by making use of protected objects and ceiling priorities.

# 4.3 Protected object's priority ceiling

Protected objects have a static priority ceiling. A locking policy describes the details how protected objects are locked in relation with tasks. The predefined locking policy Ceiling\_Locking determines that the active priority of a task cannot be higher than the ceiling priority of a protected object, when the task calls protected operations from the protected object.

When a task executes a protected action, it inherits the ceiling priority of the protected object. A calling task cannot have a higher active priority than the ceiling priority of the called protected object. Failed check leads to raising an program error.

# 4.4 Real-time tasking specialities

A useful feature in some situations in real-time programming domain is the immediate task abortion. This is called *preemptive abort* in Ada 95. A task can preempt and abort another task if needed. The implementation must document the upper time it takes to abort and verify that a task has been terminated.

An efficient and simple capability to suspend another task instead of aborting is needed in some real-time applications. Asynchronous transfer of control (ATC) means that an schedulable object's point of execution may be changed by another object. An example can be seen in Figure 2.

#### 4.5 Ravenscar profile

Tasking and other restrictions can be used in Ada 95 to prevent the use of unsafe language features. If the general run-time model of Ada would cause extensive costs or unsafety, a subset of its features can be taken into use with the pragma Restrictions.

By using the *Ravenscar profile* [1], applications can be guaranteed to be deterministic. They can be analyzed by static program analysis tools. When using this profile, for example the use of rendezvous in task communication (explained below) is prohibited.

```

with Ada. Text_IO; use Ada. Text_IO;

procedure Get_Name is

Name : String (1..80);

Length: Integer;

begin

select

delay 5.0;

New_Line;

Put_Line ("You are too slow.");

then abort

Put ("Enter your name in 5s:

Get_Line (Name, Length);

Put ("Hello, ");

Put (Name (1..Length));

end select;

end Get_Name;

```

Figure 2. Delay statement and asynchronous transfer of control

### 4.6 Code predictability

As mentioned before, real-time scheduler needs static timing information to operate correctly. This is highly essential in the hard real-time environments. Worst case execution time (WCET)-analysable sporadic hard real-time tasks can be implemented in Ada as described in [2]. This is done run-time by using Deadline Monotonic Scheduling Analysis instead of too heavy Rate Monotonic Analysis. WCET calculation has also been researched e.g. in [3].

In general, elapsed time measurement and precise periodic execution are established by Real\_Time.Time and delay statement. Also, certain restrictions must be taken in to use that are described later on.

# 5 Memory management

Ada 95 does not provide automatic garbage collection for the programmer. However, compilers may provide an implementation of this feature. As this will cause unpredictability in the execution time and space, it is not very usable in the real-time programming domain.

The memory can be dynamically reserved at with a reserved word *new*. It is called an *allocator* and it reserves memory at run time for an object of some type. Pointer arithmetics are by default prohibited in Ada contrary to, for example, C or C++. This is a partial result from the requirement to minimize side effects in the language. Dynamically allocated areas of memory are handled by the package System. Storage\_Pools that is described in Chapter 13 of [7].

Ada run-time executives usually map into the underlying operating systems on memory management. Ada 95 can make use of the underlying real-time operating system (RTOS). It is implementation dependant, what can be done real-time. Usually, hard real-time programs need to be very deterministic on memory usage and there is little need for large scale dynamic memory allocation and deallocation.

#### 6 Communication

In this chapter, communication is divided into two levels. First, inter-process communication in the Ada 95 language is described. Next, more general level of interaction with the real world is described. Input/output is a critical part in real-time environments as this is the part where the real-time programming links with the real world.

#### 6.1 Inter-process communication

Tasks in Ada communicate with each other usually with rendezvous. A task that wishes to communicate with another task places a request for rendezvous in the entry queue of the called task. Then the calling task is suspended until the request for this anonymous rendezvous, or entry, in the queue is consumed and the called task has processed this entry. However, the calling task may as a part of the call ask that the request will remain in the queue only for a limited period of time.

Additional to the direct communication mechanism rendezvous, indirect communication is possible by using

```

pragma Task_Dispatching_Policy(

FIFO_Within_Priorities);

Package Position is

Sens_Int_Lvl : constant := 15;

protected Value is

procedure Sensor;

pragma Interrupt_Priority(Sens_Int_Lvl);

pragma Interrupt_Handler(Sensor);

pragma Attach_Handler(Sensor,

Sens_Int_Lvl);

procedure Get_Value(Value :

out Interfaces.Integer_32);

private

Value : Interfaces.Integer_32;

end Value;

end Position;

```

Figure 3. Example of an protected object and an interrupt handler

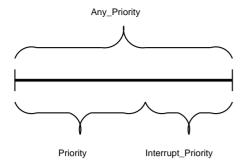

Figure 4. Ada priorities

shared data or protected objects. Rendezvous has been thought to be too complicated to be properly statically analyzed and is prohibited in some language restrictions as described above.

# 6.2 Input/Output

The Systems Programming Annex (Annex C) provides many low-level programming features. For example, it is possible to access memory directly by an address and interrupt handlers can be programmed. An code sketch of the latter can be seen in Figure 3.

The package Ada.Real\_Time provides that accurate time sources can be used. A task may delay itself accurately as was seen in Figure 2. A single time unit must be less than 20 microseconds. Numerous of details of time are considered to be documented, such as the upper bound on clock drift rate.

The different interrupt subtypes can bee seen in Figure 4. The Interrupt\_Priority is typically higher than a Priority of a task so that a task would not block an interrupt. The minimum level of interrupts that need to be supported by the hardware is 31.

The low-level programming is not so dangerous as it is in, for example, C. There are no true pointers in Ada. A corresponding capability is achieved with *access types*. They are safe by default, there are no void pointers.

Programming at the machine level is possible by deal with addresses and raw storage as shown in example in Figure 5. Also, Ada 95 programs can interface with native code, if necessary. Subprograms can be written that have inlined assembler code with the package System. Machine\_Code.

# 7. Conclusions

This article has given a brief introduction what real-time programming is like using Ada 95. It can be said that Ada 95 is a language suitable for real-time programming.

Read\_Value : Interfaces.Integer\_32;

for Read\_Value'Address use

System.Storage\_Elements.

To\_Address(16#1024);

# Figure 5. Reading an integer from a memory address

The built-in facilities to support real-time programming are quite rare among other languages. Ada was designed to promote sound software engineering practices from the beginning. It has a high performance and an encapsulated tasking model.

The descrease of popularity seems to be the biggest risk in using Ada 95. It is much more harder to find skilled Ada programmers than, for example, adept C staff. Therefore, it is also increasingly hard to find supported compilers and platforms to be used in real-time programming. The future of the language itself does not seem to depend critically on the newcoming reversion of the language, Ada 0Y.

#### References

- [1] A. Burns. The ravenscar profile. *Ada Lett.*, XIX(4):49–52, 1999.

- [2] A. Burns and A. J. Wellings. Implementing analysable hard real-time sporadic tasks in Ada 9X. ACM SIGADA Ada Letters, 14(1):38–49, /1994.

- [3] R. Chapman, A. Burns, and A. Wellings. Static worst-case timing analysis of ada. Ada Lett., XIV(5):88–91, 1994.

- [4] M. B. Feldman. Who's Using Ada? Real-World Projects Powered by the Ada Programming Language, August 2002. Webpage. Referenced in October 2004. http://www.seas.gwu.edu/~mfeldman/ ada-project-summary.html.

- [5] International Standard ISO/IEC 8652:1995(E) with COR.1:2000. Ada 95 Rationale: The Language, the Standard Libraries, 1997. Lecture Notes in Computer Science, 1247.

- [6] International Standard ISO/IEC 8652:1995(E) with COR.1:2000. Ada95 Language Reference Manual, 2000. Version 6.0.

- [7] International Standard ISO/IEC 8652:1995(E) with COR.1:2000. Annotated Ada95 Language Reference Manual: Language and Standard Libraries, 2000. The MITRE Corporation, Inc.

- [8] R. Riehle. Ada Distilled: An Introduction to Ada Programming for Experienced Computer Programmers. AdaWorks Software Engineering, 2003.

- [9] L. Sha and J. B. Goodenough. Real-Time Scheduling Theory and Ada. *Computer*, 23(4):53–62, 1990.

# Using Rational Rose and Rational Rose RT in Real-Time Development

Timo Toivanen

Helsinki University of Technology

Computer Science Laboratory

Timo.Toivanen@iki.fi

#### **Abstract**

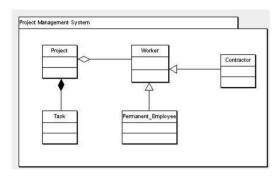

Using modeling software and automatic code generators instead of writing code from scratch has been an option for some time at least in technically less demanding programs but now it is taking foothold also in real-time development. Using generated code will help to avoid many nasty caveats and it will speed up the development process. UML-based code generators do still have problems in real-time domain, but the solution exists. This article will give a short introduction to two code generation tools and describe some of concepts related to these tools.

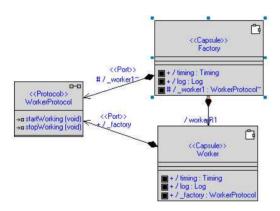

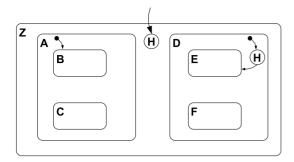

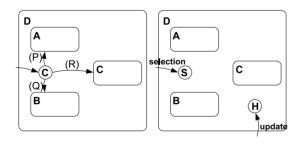

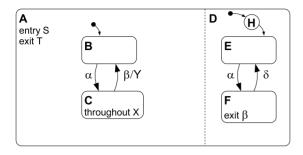

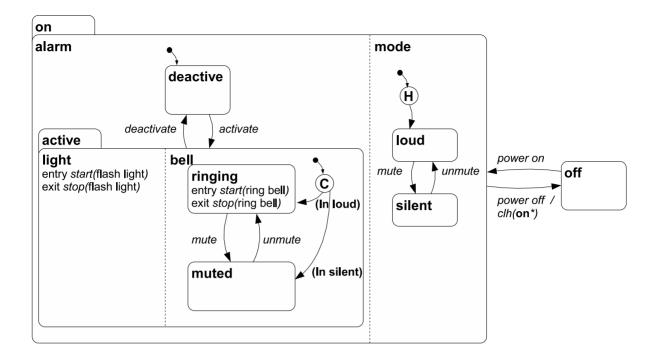

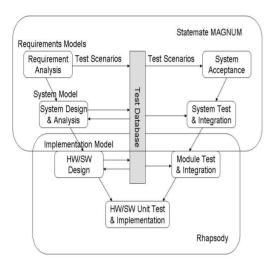

#### 1 Introduction